# NITX-300-ET-DVI

Installation and Use P/N: 6806800N97B August 2014

© Copyright 2014 Artesyn Embedded Technologies, Inc.

All rights reserved.

#### **Trademarks**

Artesyn Embedded Technologies, Artesyn and the Artesyn Embedded Technologies logo are trademarks and service marks of Artesyn Embedded Technologies, Inc. <sup>©</sup> 2014 Artesyn Embedded Technologies, Inc. All other product or service names are the property of their respective owners.

$Intel \\ ^{\textcircled{\$}} is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.$

Java <sup>™</sup> and all other Java-based marks are trademarks or registered trademarks of Oracle America, Inc. in the U.S. and other countries.

Microsoft $^{\mathbb{B}}$ , Windows $^{\mathbb{B}}$  and Windows Me $^{\mathbb{B}}$  are registered trademarks of Microsoft Corporation; and Windows XP $^{\mathbb{M}}$  is a trademark of Microsoft Corporation.

$PICMG^{\$}$ ,  $CompactPCI^{\$}$ ,  $AdvancedTCA^{TM}$  and the PICMG, CompactPCI and AdvancedTCA logos are registered trademarks of the PCI Industrial Computer Manufacturers Group.

UNIX<sup>®</sup> is a registered trademark of The Open Group in the United States and other countries.

#### Notice

While reasonable efforts have been made to assure the accuracy of this document, Artesyn assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Artesyn reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Artesyn to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to an Artesyn website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Artesyn.

It is possible that this publication may contain reference to or information about Artesyn products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Artesyn intends to announce such Artesyn products, programming, or services in your country.

#### **Limited and Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Artesyn.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

#### **Contact Address**

Artesyn Embedded Technologies Marketing Communications 2900 S. Diablo Way, Suite 190 Tempe, Arizona 85282 Artesyn Embedded Technologies Lilienthalstr. 17-19 85579 Neubiberg/Munich Germany

# **Contents**

| Ab | About this Manual |                                                            |    |  |

|----|-------------------|------------------------------------------------------------|----|--|

| 1  | Intro             | oduction                                                   | 15 |  |

|    | 1.1               | Overview                                                   | 15 |  |

|    | 1.2               | Standard Compliances                                       |    |  |

|    | 1.3               | Mechanical Data                                            |    |  |

|    |                   | 1.3.1 NITX-300-ET-DVI Mechanical Data                      | 18 |  |

|    | 1.4               | Board Identification                                       | 19 |  |

|    | 1.5               | Ordering Information                                       | 20 |  |

|    |                   | 1.5.1 Board Variants                                       | 20 |  |

|    |                   | 1.5.2 Board Accessories                                    | 20 |  |

| 2  | Haro              | lware Preparation and Installation                         | 21 |  |

|    | 2.1               | Environmental and Power Requirements                       | 21 |  |

|    |                   | 2.1.1 Environmental Requirements                           |    |  |

|    |                   | 2.1.2 Thermal Requirements                                 |    |  |

|    |                   | 2.1.3 Power Requirements                                   |    |  |

|    | 2.2               | Unpacking and Inspecting the Board                         |    |  |

|    | 2.3               | Preparing the Installation Environment                     | 24 |  |

|    | 2.4               | Board Thermal Management and Placement                     | 25 |  |

|    | 2.5               | eUSB Flash Disk Installation and Removal                   | 28 |  |

|    | 2.6               | SATA HDD and Slim Lite SSD (MO-297) Connection and Removal | 29 |  |

| 3  | Cont              | trols, LEDs, and Connectors                                | 33 |  |

|    | 3.1               | Board Layout                                               | 33 |  |

|    | 3.2               | Connectors and Switches                                    | 35 |  |

|    |                   | 3.2.1 LVDS Header (P28)                                    | 35 |  |

|    |                   | 3.2.2 LVDS Backlight Header (P23)                          | 35 |  |

|    |                   | 3.2.3 LVDS Power Header (P5)                               | 36 |  |

|    |                   | 3.2.4 USB client header (P18)                              | 36 |  |

|    |                   | 3.2.5 USB Header (P6)                                      |    |  |

|    |                   | 3.2.6 eUSB Header (P2)                                     | 37 |  |

|    |                   | 3.2.7 Audio Header (P12)                                   | 38 |  |

|    |                   | 3.2.8 CAN Bus Header (P15)                                 | 38 |  |

|    |                   |                                                            |    |  |

#### Contents

|   |      | 3.2.9 Full Wire RS232 Header (P7)  | 39 |

|---|------|------------------------------------|----|

|   |      | 3.2.10 Two Wire RS232 Header (P14) | 39 |

|   |      | 3.2.11 Battery Socket (XBT1)       | 40 |

|   |      | 3.2.12 Front Panel Header (P19)    | 40 |

|   |      | 3.2.13 GPIO Header (P4)            |    |

|   |      | 3.2.14 CPU FAN Header (P1)         | 42 |

|   |      | 3.2.15 SATA Power Header (P16)     | 42 |

|   |      | 3.2.16  9 SATA Connector           | 42 |

|   | 3.3  | Onboard LEDs                       | 44 |

| 4 | Func | tional Description                 | 45 |

|   | 4.1  | Block Diagram                      | 45 |

|   | 4.1  | Processor                          |    |

|   | 4.2  | System Memory                      |    |

|   | 4.3  | PCI-E Port                         |    |

|   | 4.4  | SATA                               |    |

|   | 4.5  | MicroSD                            |    |

|   | 4.7  | Ethernet Interfaces                |    |

|   | 4.7  | USB Interface                      |    |

|   | 4.9  | USB Flash                          |    |

|   |      | RS-232                             |    |

|   |      | CAN bus                            |    |

|   |      | I2C Serial Interface and Devices   |    |

|   |      | Video Interface                    |    |

|   |      | Audio Interface                    |    |

|   |      | BIOS Device                        |    |

|   |      | GPIO Configuration                 |    |

|   |      | Clock Distribution                 |    |

|   | 4.17 | Clock Distribution                 | 57 |

| 5 | BIOS |                                    | 59 |

|   | 5.1  | POST                               | 59 |

|   | 5.2  | Boot Process                       |    |

|   | 5.3  | Initiating Setup                   |    |

|   | 5.4  | Setup Utility                      |    |

|   |      |                                    |    |

|   |            | 5.4.1    | Main Me     | enu                                                 | 62  |

|---|------------|----------|-------------|-----------------------------------------------------|-----|

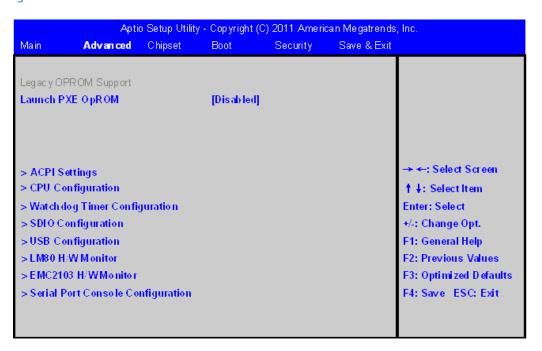

|   |            | 5.4.2    | Advance     | ed Menu                                             | 64  |

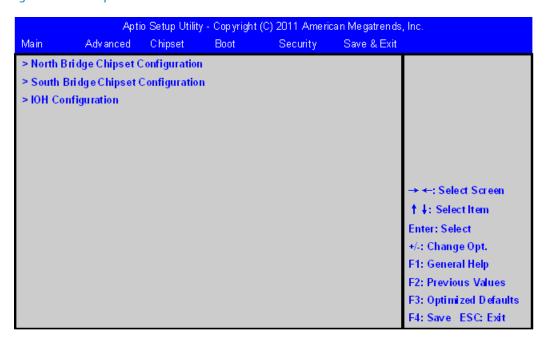

|   |            | 5.4.3    | Chipset N   | Menu                                                | 70  |

|   |            | 5.4.4    | Boot Mei    | nu                                                  | 72  |

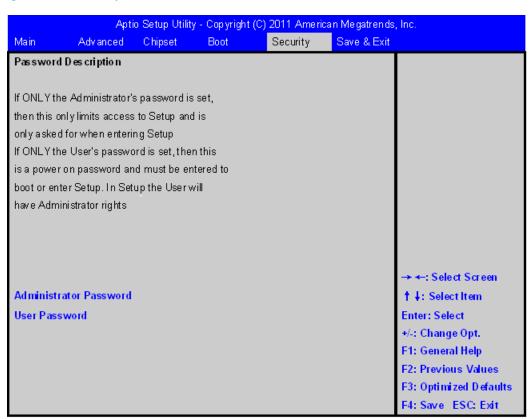

|   |            | 5.4.5    | Security    | Menu                                                | 74  |

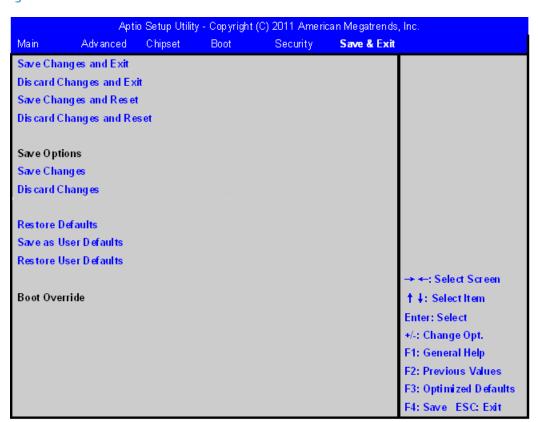

|   |            | 5.4.6    | Save and    | d Exit Menu                                         | 75  |

|   | 5.5        | POST     | Codes       |                                                     | 76  |

|   |            | 5.5.1    | Status Co   | ode Ranges                                          | 76  |

|   |            | 5.5.2    | Standard    | d Status Codes                                      | 77  |

|   |            |          | 5.5.2.1     | SEC Status Codes                                    | 77  |

|   |            |          | 5.5.2.2     | PEI Status Codes                                    | 78  |

|   |            |          | 5.5.2.3     | PEI Beep Codes                                      | 81  |

|   |            |          | 5.5.2.4     | DXE Status Codes                                    | 82  |

|   |            |          | 5.5.2.5     | DXE Beep Codes                                      | 85  |

|   |            |          | 5.5.2.6     | CPU Exception Status Codess                         | 85  |

|   |            |          | 5.5.2.7     | ASL Status Codes                                    |     |

|   |            |          | 5.5.2.8     | OEM-reserved Status Code Ranges                     | 87  |

|   | 5.6        | Boot (   | Order Supp  | port                                                | 87  |

|   | 5.7        | Windo    | ows XP Inst | tallation                                           | 88  |

|   | 5.8        | -        |             |                                                     |     |

|   | 5.9        | BIOS (   | Jpdate      |                                                     | 88  |

|   |            |          |             |                                                     |     |

| 6 | Ope        | rating S | System an   | nd Driver Support                                   | 91  |

|   | <i>C</i> 1 | C        | -<br>       | action of Court area                                | 0.1 |

|   | 6.1        | Suppo    | гтеа Орег   | rating Systems                                      | 91  |

|   |            |          |             |                                                     |     |

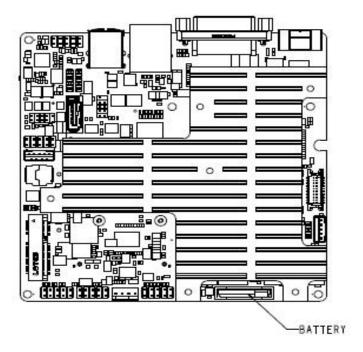

| Α | Repl       | acing t  | he Battery  | y                                                   | 93  |

|   | A.1        | Replac   | cing the Ba | attery                                              | 93  |

|   |            |          | 5           | ,                                                   |     |

| В | Rela       | ted Do   | cumentati   | ion                                                 | 95  |

|   |            |          |             |                                                     |     |

|   | B.1        | Artesy   | n Embedd    | ded Technologies - Embedded Computing Documentation | 95  |

#### Contents

| Safety Notes        | <br> | <br>97 |

|---------------------|------|--------|

| Sicherheitshinweise |      | <br>   |

# List of Tables

| Table 1-1  | Key Features of the NITX-300-ET-DVI            | 15 |

|------------|------------------------------------------------|----|

| Table 1-2  | Board Standard Compliances                     | 17 |

| Table 1-3  | Available Board Variants                       | 20 |

| Table 1-4  | Available Board Accessories                    | 20 |

| Table 2-1  | Environmental Requirements of NITX-300-ET-DVI  | 21 |

| Table 2-2  | Critical temperature Spots for NITX-300-ET-DVI | 22 |

| Table 2-3  | NITX-300-ET-DVI Power Dissipation              | 23 |

| Table 2-4  | Onboard LED Definition                         | 27 |

| Table 3-1  | LVDS Header Pin Definition (P28)               | 35 |

| Table 3-2  | LVDS Inverter Header Pin Definition            | 35 |

| Table 3-3  | LVDS Power Connector Pin Definition            | 36 |

| Table 3-4  | LVDS Power Jumper Pin Definition               | 36 |

| Table 3-5  | USB Client Header Pin Definition               | 36 |

| Table 3-6  | USB Header Pin Definition                      | 37 |

| Table 3-7  | eUSB Pin Header Definition                     | 37 |

| Table 3-8  | Audio Header Pin Definition                    |    |

| Table 3-9  | CAN Bus Header Pin Definition                  | 38 |

| Table 3-10 | Full Wire RS232 Header Pin Definition          |    |

| Table 3-11 | Two Wire RS232 Header                          | 39 |

| Table 3-12 | Battery Header Pin Definition                  |    |

| Table 3-13 | Front Panel Header Pin Definition              | 40 |

| Table 3-14 | GPIO Header Pin Definition                     | 41 |

| Table 3-15 | CPU FAN Header Pin Definition                  | 42 |

| Table 3-16 | SATA Power Header Pin Definition               | 42 |

| Table 3-17 | J9 SATA Pin Definition                         | 42 |

| Table 3-18 | Onboard LEDs                                   |    |

| Table 4-1  | Tunnel Creek Processor Features                | 46 |

| Table 4-2  | I2C Device Address                             | 53 |

| Table 4-3  | TNC GPIO Definition                            |    |

| Table 4-4  | Topcliff GPIO Configuration                    | 55 |

| Table 4-5  | Clock Assignments                              |    |

| Table 5-1  | BIOS Primary Menu                              |    |

| Table 5-2  | Aptio Navigation                               |    |

| Table 5-3  | Main Menu Field Description                    |    |

| Table 5-4  | Platform Information                           |    |

| Table 5-5  | Advanced Menu Field Description                | 64 |

|            |                                                |    |

#### List of Tables

| Table 5-6  | ACPI Settings                                                   | 65 |

|------------|-----------------------------------------------------------------|----|

| Table 5-7  | CPU Configuration                                               | 65 |

| Table 5-8  | Watchdog Timer Configuration                                    | 66 |

| Table 5-9  | SDIO Configuration                                              | 66 |

| Table 5-10 | USB Configuration                                               | 66 |

| Table 5-11 | LM80 H/W Monitor                                                | 67 |

| Table 5-12 | EMC2103 H/W Monitor                                             | 67 |

| Table 5-13 | Serial Port Console Redirection                                 | 68 |

| Table 5-14 | COM0 Console Redirection Settings                               | 69 |

| Table 5-15 | Chipset Menu Field Descriptions                                 | 70 |

| Table 5-16 | North Bridge Chipset Configuration                              | 70 |

| Table 5-17 | Boot Display Configuration                                      | 71 |

| Table 5-18 | IOH Configuration                                               | 71 |

| Table 5-19 | Wake On Lan Configuration                                       | 72 |

| Table 5-20 | Boot Menu Field Description                                     | 73 |

| Table 5-21 | Security Menu Field Description                                 | 74 |

| Table 5-22 | Save and Exit Menu Field Description                            | 75 |

| Table 5-23 | Status Code Ranges                                              | 76 |

| Table 5-24 | SEC Status Codes                                                | 77 |

| Table 5-25 | PEI Status Codes                                                | 78 |

| Table 5-26 | PEI Beep Codes                                                  | 81 |

| Table 5-27 | DXE Status Codes                                                | 82 |

| Table 5-28 | DXE Beep Codes                                                  | 85 |

| Table 5-29 | CPU Exception Status Codes                                      |    |

| Table 5-30 | ASL Status Codes                                                | 86 |

| Table 5-31 | OEM-reserved Status Code Ranges                                 | 87 |

| Table R-1  | Artesyn Embedded Technologies - Embedded Computing Publications | 95 |

# List of Figures

| Figure 1-1 | NITX-300-ET-DVI Mechanical Data (Top View)    | 18 |

|------------|-----------------------------------------------|----|

| Figure 1-2 | NITX-300-ET-DVI Mechanical Data (Side View)   | 19 |

| Figure 1-3 | Serial Number Location                        | 19 |

| Figure 2-1 | Board Thermal Management Diagram              | 26 |

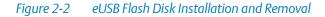

| Figure 2-2 | eUSB Flash Disk Installation and Removal      | 28 |

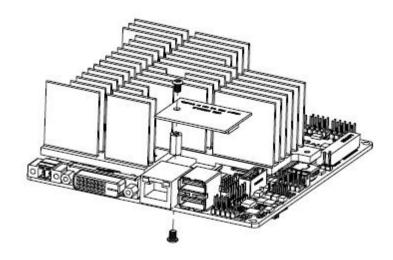

| Figure 2-3 | J9 22-pin SATA connector                      | 29 |

| Figure 2-4 | Serial ATA HDD                                | 30 |

| Figure 2-5 | Slim Lite SSD (MO-297)                        | 31 |

| Figure 3-1 | NITX-300-ET-DVI Module Components             | 33 |

| Figure 3-2 | NITX-300-ET-DVI Module Components (Rear View) | 34 |

| Figure 4-1 | Block Diagram for NITX-300-ET-DVI             | 45 |

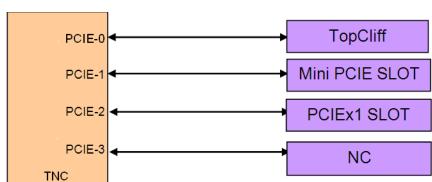

| Figure 4-2 | PCI-E Connection Diagram                      | 48 |

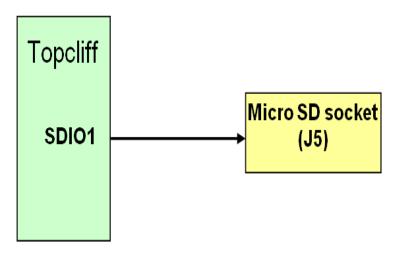

| Figure 4-3 | SDIO Link Connection Diagram                  | 49 |

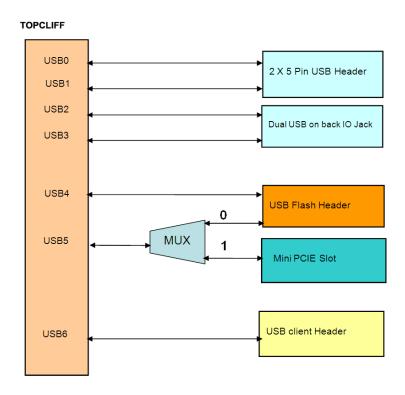

| Figure 4-4 | USB ports connections diagram                 | 50 |

| Figure 4-5 | USB Flash Connector Pin Definition            | 51 |

| Figure 4-6 | Board I2C Device Connection Diagram           | 53 |

| Figure 4-7 | Clock Distribution of NITX-300-ET-DVI         | 57 |

| Figure 5-1 | Main Menu                                     | 62 |

| Figure 5-2 | Advanced Menu                                 |    |

| Figure 5-3 | Chipset Menu                                  | 70 |

| Figure 5-4 | Boot Menu                                     | 72 |

| Figure 5-5 | Security Menu                                 | 74 |

| Figure 5-6 | Save and Exit Menu                            |    |

| Figure A-1 | Battery Location                              | 93 |

List of Figures

# **About this Manual**

#### **Overview of Contents**

This manual is divided into the following chapters and appendices.

- *Introduction* gives an overview of the features of the product, standard compliances, mechanical data, and ordering information.

- Hardware Preparation and Installation outlines the installation requirements, hardware accessories, switch settings, and installation procedures.

- Controls, LEDs, and Connectors describes external interfaces of the board. This include connectors and LEDs.

- Functional Description includes a block diagram and functional description of major components of the product.

- Replacing the Battery contains the procedures for replacing the battery.

- *Related Documentation* provides a listing of related product documentation, manufacturer's documents, and industry standard specifications.

- Safety Notes summarizes the safety instructions in the manual.

- Sicherheitshinweise is a German translation of the Safety Notes chapter.

#### **Abbreviations**

This document uses the following abbreviations:

| TERM   | MEANING                                                                                                     |

|--------|-------------------------------------------------------------------------------------------------------------|

| Α      | Amps                                                                                                        |

| AC '97 | Audio CODEC (Coder-Decoder)                                                                                 |

| AHCI   | Advanced Host Controller Interface                                                                          |

| ACPI   | Advanced Configuration Power Interface - software standard to implement power saving modes in PC-AT systems |

| BDS    | Boot Device Selection                                                                                       |

| CAN    | Controller Area Network                                                                                     |

| DAR    | Disabled Automatic Retransmission                                                                           |

| TERM         | MEANING                                                                                                                                                                                                                     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DXE          | Driver eXecution Environment                                                                                                                                                                                                |

| EEPROM       | Electrically Erasable Programmable Read-Only Memory                                                                                                                                                                         |

| FCBGA        | Flip Chip Ball Grid Array                                                                                                                                                                                                   |

| GPI          | General Purpose Input                                                                                                                                                                                                       |

| GPIO         | General Purpose Input Output                                                                                                                                                                                                |

| GPO          | General Purpose Output                                                                                                                                                                                                      |

| HDA          | High Definition Audio                                                                                                                                                                                                       |

| I2C          | Inter Integrated Circuit - 2 wire (clock and data) signaling scheme allowing communication between integrated circuits, primarily used to read and load registers values.                                                   |

| IDE          | Integrated Device Electronics - parallel interface for hard disk drives - also known as PATA                                                                                                                                |

| IOH          | IO Hub                                                                                                                                                                                                                      |

| LPC          | Low Pin-Count Interface: a low speed interface used for peripheral circuits such as Super I/O controllers, which typically combine legacy-device support into a single IC.                                                  |

| LVDS         | Low Voltage Differential Signaling - widely used as a physical interface for TFT flat panels. LVDS can be used for many high-speed signaling applications. In this document, it refers only to TFT flat-panel applications. |

| MSR          | Model Specific Registers                                                                                                                                                                                                    |

| PCI          | Peripheral Component Interface                                                                                                                                                                                              |

| PCI-E        | Peripheral Component Interface Express - next-generation high speed Serialized I/O bus                                                                                                                                      |

| PEI          | Pre-EFI Initialization                                                                                                                                                                                                      |

| PHY          | Ethernet controller physical layer device                                                                                                                                                                                   |

| Pin-out Type | A reference to one of five COM ExpressTM definitions for what signals appear on the COM ExpressTM module connector pins.                                                                                                    |

| RGMII        | Reduced Gigabit Media Independent Interface                                                                                                                                                                                 |

| SM           | System Management                                                                                                                                                                                                           |

| SPD          | Serial Presence Detect - refers to serial EEPROM on DRAMs that has DRAM module configuration information                                                                                                                    |

| TERM | MEANING                                                                                  |

|------|------------------------------------------------------------------------------------------|

| SPI  | Serial Peripheral Interface                                                              |

| SATA | Serial AT Attachment: serial-interface standard for hard disks                           |

| SDVO | Serialized Digital Video Output - Intel defined format for digital video output that can |

| TPM  | Trusted Platform Module                                                                  |

| VGA  | Video Graphics Adapter                                                                   |

| WDT  | Watch Dog Timer                                                                          |

# **Conventions**

The following table describes the conventions used throughout this manual.

| Notation       | Description                                                                                                   |

|----------------|---------------------------------------------------------------------------------------------------------------|

| 0x00000000     | Typical notation for hexadecimal numbers (digits are 0 through F), for example used for addresses and offsets |

| 0Ь0000         | Same for binary numbers (digits are 0 and 1)                                                                  |

| bold           | Used to emphasize a word                                                                                      |

| Screen         | Used for on-screen output and code related elements or commands in body text                                  |

| Courier + Bold | Used to characterize user input and to separate it from system output                                         |

| Reference      | Used for references and for table and figure descriptions                                                     |

| File > Exit    | Notation for selecting a submenu                                                                              |

| <text></text>  | Notation for variables and keys                                                                               |

| [text]         | Notation for software buttons to click on the screen and parameter description                                |

|                | Repeated item for example node 1, node 2,, node 12                                                            |

| Notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Description                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| ·<br>·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Omission of information from example/command that is not necessary at the time being           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ranges, for example: 04 means one of the integers 0,1,2,3, and 4 (used in registers)           |

| I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Logical OR                                                                                     |

| **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Indicates a hazardous situation which, if not avoided, could result in death or serious injury |

| A CAUTION  DOCCODDOCCODOCOCICODOCOCICODOCOCICODOCOCICODOCOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCICODOCI | Indicates a hazardous situation which, if not avoided, may result in minor or moderate injury  |

| NOTICE  XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Indicates a property damage message                                                            |

| **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | No danger encountered. Pay attention to important information                                  |

# **Summary of Changes**

This manual has been revised and replaces all prior editions.

| Part Number | Publication Date | Description                     |

|-------------|------------------|---------------------------------|

| 6806800N97A | February 2012    | Initial release                 |

| 6806800N97B | August 2014      | Re-branded to Artesyn template. |

# Introduction

#### 1.1 Overview

NITX-300-ET-DVI is a highly integrated small form factor Nano-ITX board based on the Queensbay platform, including the Tunnel Creek processor and Topcliff IOH. The NITX-300-ET-DVI incorporates the standard processor, memory, graphics and I/O functionality, as is common to a small form factor PC motherboard. The NITX-300-ET-DVI operates with or without a local display. Standard PC expansion ports are also available on the rear panel along with additional USB ports, SATA and Low Voltage Differential Signaling (LVDS) via headers on the board as well as a single PCI Express expansion slot. As the NITX-300-ET-DVI is based on the latest Intel Queensbay platform, it has a long product life cycle, lower power consumption and suitable for fanless applications. NITX-300-ET-DVI performs well within extended temperature ranges for more rugged commercial applications. NITX-300-ET-DVI is designed to meet -40 °C to -85 °C ambient temperature requirement.

Table 1-1 Key Features of the NITX-300-ET-DVI

| Function     | Features                                                                                                                         |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Processor    | Intel Tunnel Creek processor E620T 0.6GHz                                                                                        |  |

|              | Single channel memory controller supporting DDR2 800 MT/s memory down                                                            |  |

|              | Both LVDS up to 1280x768 @ 60Hz and Serialized Digital Video Output (SDVO) output up to 1280x1024 @ 85Hz output support          |  |

|              | <ul> <li>Four x1 lane PCI Express (PCI-E) root ports supporting the PCI<br/>Express Base Specification, Revision 1.0a</li> </ul> |  |

|              | Implements an Low Pin-Count (LPC) interface as described in the LPC1.1 specification                                             |  |

|              | SMBus host controller based on Version 1.0 support                                                                               |  |

|              | Serial Peripheral Interface (SPI)                                                                                                |  |

|              | Integrated Watch Dog Timer (WDT)                                                                                                 |  |

| IO Hub (IOH) | Intel Topcliff IOH                                                                                                               |  |

| BIOS Device  | One 4MB SPI boot device                                                                                                          |  |

| Memory       | Supports 512MB 32-bit DDR2 800 MHz non-ECC memory down on<br>NITX-300-ET-DVI                                                     |  |

| eUSB flash   | An optional eUSB flash on one 2x5 header on board                                                                                |  |

| PCI-E        | One PCI-E x1 slot                                                                                                                |  |

|              | One mini PCI-E socket                                                                                                            |  |

Table 1-1 Key Features of the NITX-300-ET-DVI (continued)

| Function                             | Features                                                                                                                                                                                          |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SATA                                 | <ul> <li>One internal SATA connector (7-pin)</li> <li>One standard 22 (15power+7signal) pins SATA connector for JEDEC MOS-297A internal slim lite SDD application</li> </ul>                      |  |

| MicroSD Card                         | One Micro SD card slot                                                                                                                                                                            |  |

| USB                                  | Two Hi-Speed USB 2.0 interfaces to USB 2.0 Type A connectors accessible in the back-panel I/O region                                                                                              |  |

|                                      | <ul> <li>Four Hi-Speed USB 2.0 interfaces to two 9-pin dual-USB headers,<br/>one is optionally connecting mini PCI-E slot</li> </ul>                                                              |  |

|                                      | One USB client port on an internal header                                                                                                                                                         |  |

| Ethernet                             | Supports 10/100/1000 Ethernet based on Marvell 88E1111                                                                                                                                            |  |

| RS232                                | <ul> <li>One full signal (8-wire) COM through RS-232 transceiver to header</li> <li>Three UART (2-wire) through RS-232 transceiver to one internal header</li> </ul>                              |  |

| Controller Area Network<br>(CAN) bus | One set of CAN bus on one 4-pin internal header                                                                                                                                                   |  |

| Video                                | <ul> <li>One single-channel LVDS 20-pin header</li> <li>One DVI port derived from the SDVO port</li> </ul>                                                                                        |  |

| Audio                                | One High Definition Audio (HDA) codec with one Line-in, one Line-out port                                                                                                                         |  |

| Watchdog                             | One integrated watchdog with sepectable options from approximately 1 minute to 10 minutes                                                                                                         |  |

| Form factor                          | Nano-ITX , 120 mm X 120 mm form factor                                                                                                                                                            |  |

| OS                                   | <ul> <li>Supports Microsoft Windows XP Professional</li> <li>Supports Windows Embedded Standard 7</li> <li>Supports Windows Embedded Standard 2009</li> <li>Supports Timesys Fedora 14</li> </ul> |  |

| Temperature                          | ● -40 °C to +85 °C                                                                                                                                                                                |  |

# 1.2 Standard Compliances

This product is designed to meet the following standards.

Table 1-2 Board Standard Compliances

| Standard                 | Description                                                                                                                                      |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| EMC Compliance Standards | FCC 47 CFR Part 15 Subpart B (US) Class B; AS/NZS CISPR 22 Class B (Australia/New Zealand); VCCI Class B (Japan); EN55022 Class B (EU); EN55024. |

| Safety Standards         | UL/CSA No. 60950-1; IEC 60950-1 CB Scheme; EN 60950-1; AS/NZS-60950-1.                                                                           |

# 1.3 Mechanical Data

#### 1.3.1 NITX-300-ET-DVI Mechanical Data

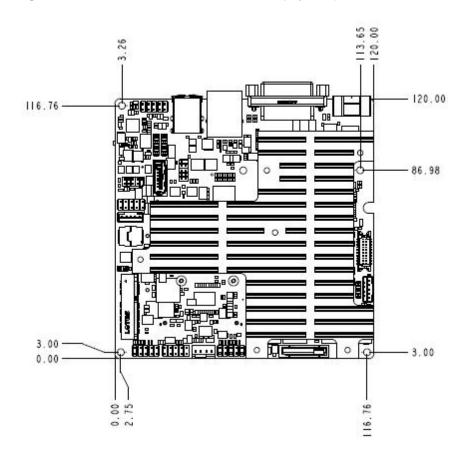

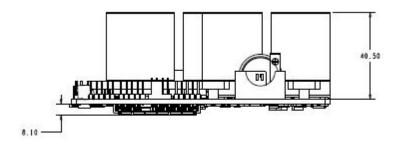

Figure 1-1 NITX-300-ET-DVI Mechanical Data (Top View)

Figure 1-2 NITX-300-ET-DVI Mechanical Data (Side View)

# 1.4 Board Identification

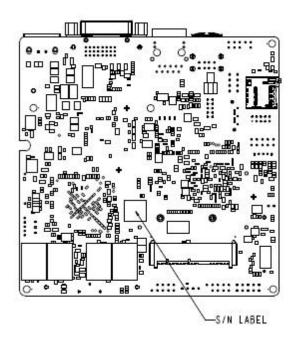

This section shows the serial number and its location on the board.

Figure 1-3 Serial Number Location

# 1.5 Ordering Information

Use the order numbers below when ordering board variants or board accessories.

#### 1.5.1 Board Variants

The following table lists the product variants that are available upon release of this publication.

#### Table 1-3 Available Board Variants

| Part Number     | Description                                                               |

|-----------------|---------------------------------------------------------------------------|

| NITX-300-ET-DVI | Nano-ITX motherboard with 600MHz E620T, 512MB, DVI, Extended temperature. |

#### 1.5.2 Board Accessories

The following table lists the board accessories that are available upon release of this publication.

Table 1-4 Available Board Accessories

| Order Number | Description          |

|--------------|----------------------|

| KR8-PS01     | DC POWER ADAPTER 60W |

|              | 9-pin serial cable   |

# **Hardware Preparation and Installation**

### 2.1 Environmental and Power Requirements

#### 2.1.1 Environmental Requirements

The following tables list the environmental requirements that NITX-300-ET-DVI board must meet when operated in your particular system configuration.

Operating temperatures refer to the temperature of the air circulating around the board and not to the component temperature.

#### **NOTICE**

**Product Damage**

High humidity and condensation on surfaces cause short circuits.

Do not operate the system outside the specified environmental limits. Make sure the product is completely dry and there is no moisture on any surface before applying power.

Table 2-1 Environmental Requirements of NITX-300-ET-DVI

| Requirement      | Operating               | Non-Operating    |

|------------------|-------------------------|------------------|

| Cooling Method   | Fanless                 |                  |

| Temp Cycle Class | -40-+85C:500cyc         |                  |

| Temperature      | -40 °C to +85 °C        | -40 °C to +85 °C |

| Humidity         | 10-90% (non-condensing) |                  |

| Vibration        | .01 g^2/Hz @ 5-500Hz    |                  |

| Shock            | 20g 11ms sine or saw    |                  |

| Altitude         | -60 - 4000 m ASL        |                  |

#### 2.1.2 Thermal Requirements

Table 2-2 Critical temperature Spots for NITX-300-ET-DVI

| Component Identifier | Heat Dissipation Power (W) | Maximum Allowable<br>Temperature (°C) |

|----------------------|----------------------------|---------------------------------------|

| CPU: Atom E620T      | 2.7                        | 110 (Tj)                              |

| IOH: EG20T           | 1.55                       | 115.7 (Tj)                            |

| Memory SDRAM 512MB   | 0.8                        | 105 (Tc)                              |

Contact your Artesyn sales representative for current information on the detailed thermal information including airflow and resistance of the board.

#### **NOTICE**

System Overheating

**Cooling Vents**

Improper cooling can lead to system damage and can void the manufacturer's warranty. To ensure proper cooling and undisturbed airflow through the system do not obstruct the ventilation openings of the system. Make sure that the fresh air supply is not mixed with hot exhaust from other devices.

#### **A** CAUTION

Personal Injury

During operation, hot surfaces may be present on the heat sinks and the components of the product.

To prevent injury from hot surface do not touch any of the exposed components or heatsinks on the product when handing. Use the handle and face plate, where applicable, or the board edge when removing the product from the enclosure.

#### 2.1.3 Power Requirements

The following table describes the power dissipation of the NITX-300-ET-DVI board.

Table 2-3 NITX-300-ET-DVI Power Dissipation

| State                          | +12 V                                               | VCC_RTC | Power consumption (w)                                |

|--------------------------------|-----------------------------------------------------|---------|------------------------------------------------------|

| G3 (AC off)                    | 0                                                   | 26.8μΑ  |                                                      |

| Idle (CMOS Setup)              | 0.8A                                                | 0       | 9.6w                                                 |

| Idle (Window XP SP3 X32)       | 0.78~0.87A                                          | 0       | 9.36w~10.44w                                         |

| FullLoading (PTU+Burn In Test) | 0.9~0.96A                                           | 0       | 10.8w~11.52w                                         |

| s5                             | 0.038A (unplug ethernet)<br>0.155 A (plug ethernet) | 0       | 0.456w (unplug<br>ethernet) 1.86w (plug<br>ethernet) |

# 2.2 Unpacking and Inspecting the Board

Read all notices and cautions prior to unpacking the product.

#### **NOTICE**

Damage of Circuits

Electrostatic discharge and incorrect installation and removal can damage circuits or shorten their life.

Before touching the board or electronic components, make sure that you are working in an ESD-safe environment.

#### **Shipment Inspection**

- 1. Verify that you have received all items of your shipment.

- 2. Check for damage and report any damage or differences to customer service.

- 3. Remove the desiccant bag shipped together with the board and dispose of it according to your country's legislation.

#### **NOTICE**

**Environmental Damage**

Improperly disposing of used products may harm the environment.

Always dispose of used products according to your country's legislation and manufacturer's instructions.

The product is thoroughly inspected before shipment. If any damage occurred during transportation or any items are missing, contact customer service immediately.

# 2.3 Preparing the Installation Environment

Before you install or replace components, pay attention to the following:

- Wear an ESD-preventive wrist strap to prevent the static electricity from damaging the device.

- Keep the area where the components reside clean and keep the components away from heat-generating devices, such as radiator.

- Ensure that your sleeves are tightened or rolled up above the elbow. For safety purposes, it is not recommended to wear jewelry, watch, glasses with metal frame, or clothes with metal buttons.

- Do not exert too much force, or insert or remove the components forcibly. Avoid damage to the components or plug-ins.

- Confirm the feasibility of the operation

There are available spare parts of the components to be installed or replaced in the equipment warehouse. When the available spare parts are lacking, contact Artesyn Embedded Technologies for help in time. For details on how to get help from Artesyn Embedded Technologies visit https://www.artesyn.com/computing.

Make sure that the new components are in good condition, without defects such as oxidation, chemical corrosion, missing components, or transportation damage.

By reading this document, you are familiar with how to install and replace the component and master the skills required by the operation.

- Check the environment

Make sure that the power supply, temperature, and humidity meet the operating

requirements for the board and its components. For details, refer to the respective system

documentation.

- Prepare the parts and the tools

Prepare the components to be installed or replaced.

When you hold or transport the components, use the special antistatic package. Prepare the cross screwdriver, screws, plastic supports, cooling gel, and ESD-preventive wrist strap.

- Confirm installation or changing position

Confirm the position where NITX-300-ET-DVI will be installed.

- If a serious problem occurs and cannot be solved when you install or replace the component, contact Artesyn Embedded Technologies for technical support.

# 2.4 Board Thermal Management and Placement

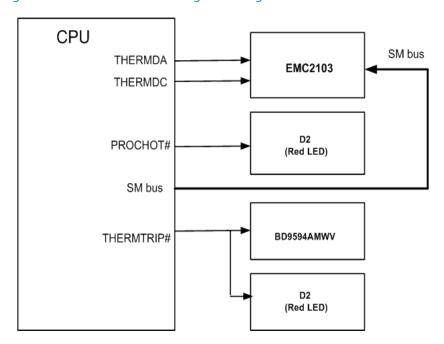

NITX-300-ET-DVI provides a thermal management strategy. This includes CPU junction temperature monitoring, one on-board fan connector, and can take the corresponding action to protect the system during catastrophic overheating.

The following diagram shows thermal management strategy:

Figure 2-1 Board Thermal Management Diagram

A PNP thermal transistor is integrated in Tunnel Creek; it is used as a diode and it connects to an external digital thermal sensor (EMC2103). The CPU can get the data of junction temperature through the System Management (SM) bus. Note that this is an inaccurate value and the temperature offset must be taken into account through the reading of the CPU's Model Specific Registers (MSR).

Intel Thermal Monitor: The Intel thermal monitor controls processor temperature by modulating (starting and stopping) the processor core clocks when the processor silicon reaches its maximum operating temperature. Signal "PROCHOT #" is used in this mode, when the processor temperature goes up to 110 °C, the PROCHOT# is output and active, it indicates that the processor thermal control circuit is activated. A red LED D2 can show the "processor hot" status.

When the CPU junction temperature is more than 125 °C, CPU will assert the THERMTRIP#, and the onboard logic will shut down the system power, the LED D8 shows this status.

Table 2-4 Onboard LED Definition

| LED | Definition                    | Status                                   | Description                           |

|-----|-------------------------------|------------------------------------------|---------------------------------------|

| D2  | 'PROCHOT' signal is active    | ON The CPU temperature goes up to 110 °C |                                       |

|     |                               | OFF                                      | Normal status                         |

| D8  | 'THERMTRIP#' signal is active | ON                                       | The CPU temperature goes up to 125 °C |

|     |                               | OFF                                      | Normal status                         |

#### 2.5 eUSB Flash Disk Installation and Removal

#### Installing the eUSB Flash Disk

1. Align and insert the connector of the eUSB flash to the connector on the NITX-300-ET-DVI module.

2. Use a M2.5x4 mm screw (0.4 N·m of torque is recommended) to fasten the eUSB flash module to the standoff.

#### Removing the eUSB Flash Disk from the Module $\,$

- 1. Loosen and remove the screws of the eUSB flash disk from the standoff.

- 2. While holding the edges, pull the eUSB flash disk from the board.

### 2.6 SATA HDD and Slim Lite SSD (MO-297) Connection and Removal

Two SATA ports are routed to the connector from the Topcliff. One port is a 7-pin SATA connector, another is a 15-power+7signals connector which is used for "Slim Lite SSD". To connect the SATA HDD and SSD, follow the steps below:

#### **NOTICE**

Damage of Circuits Electrostatic discharge and incorrect module installation and removal can damage circuits or shorten their life. Before touching the module or electronic components, make sure that you are working in an ESD-safe environment.

1. Locate the J9 22-pin SATA connector on the underside of the NITX-300-ET-DVI board.

2. Align and insert SATA HDD to the J9 22-pin SATA connector on the NITX-300-ET-DVI board.

Figure 2-4 Serial ATA HDD

HDD or SDD device should be fastened to a chassis or an enclosure.

3. Align and insert Slim Lite SSD (MO-297) to the J9 22-pin SATA connector on the NITX-300-ET-DVI board.

Use three M1.6x3.5mm screws and three M1.6x6.0mm standoffs (0.09 Nm of torque is recommended) to fasten the Slim Lite SSD (MO-297) to the NITX-300-ET-DVI board.

#### **Hardware Preparation and Installation**

# **Controls, LEDs, and Connectors**

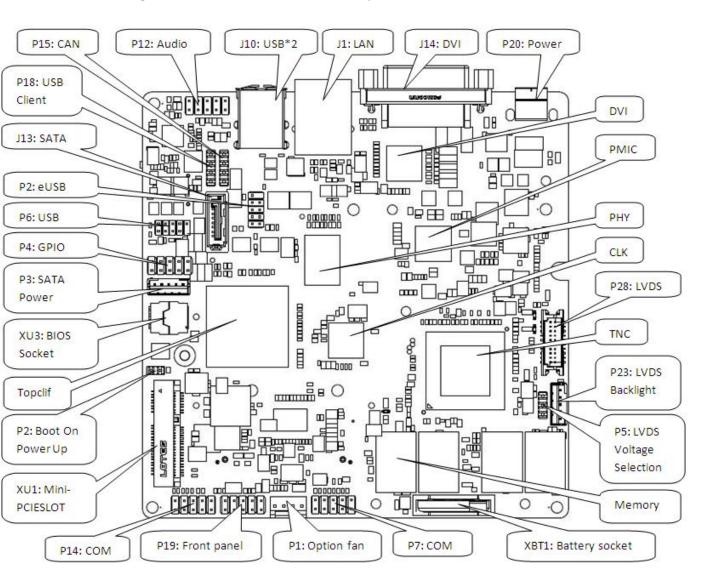

# 3.1 Board Layout

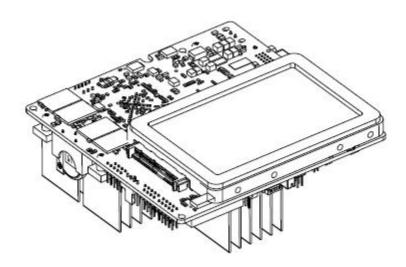

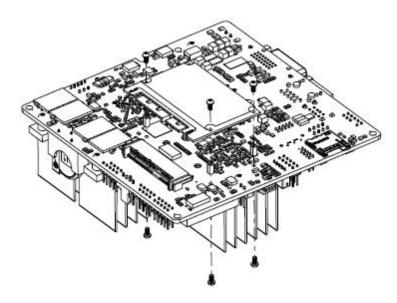

Figure 3-1 NITX-300-ET-DVI Module Components

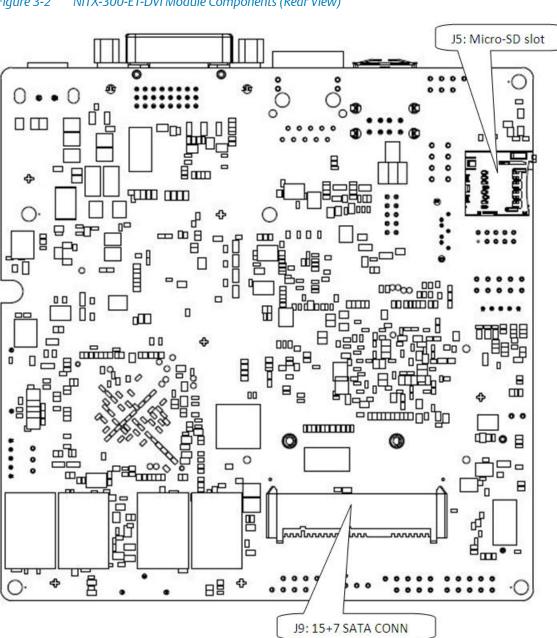

Figure 3-2 NITX-300-ET-DVI Module Components (Rear View)

### 3.2 Connectors and Switches

### 3.2.1 LVDS Header (P28)

Table 3-1 LVDS Header Pin Definition (P28)

| Pin | Signal      | Pin | Signal       |

|-----|-------------|-----|--------------|

| 1   | VCC_LVDS    | 2   | VCC_LVDS     |

| 3   | GND         | 4   | GND          |

| 5   | LVDS_A_A0_P | 6   | LVDS_A_CLK_P |

| 7   | LVDS_A_A0_N | 8   | LVDS_A_CLK_N |

| 9   | GND         | 10  | GND          |

| 11  | LVDS_A_A1_P | 12  | LDDC_CLK     |

| 13  | LVDS_A_A1_N | 14  | LDDC_DATA    |

| 15  | GND         | 16  | GND          |

| 17  | LVDS_A_A2_P | 18  | LVDS_A_A3_P  |

| 19  | LVDS_A_A2_N | 20  | LVDS_A_A3_N  |

### 3.2.2 LVDS Backlight Header (P23)

Table 3-2 LVDS Inverter Header Pin Definition

| Pin | Signal       |

|-----|--------------|

| 1   | VCC12V       |

| 2   | LVDS_BKLT_EN |

| 3   | GND          |

| 4   | LCD_BKL_ADJ  |

| 5   | VCC5V        |

### 3.2.3 LVDS Power Header (P5)

Table 3-3 LVDS Power Connector Pin Definition

| Pin | Signal       |

|-----|--------------|

| 1   | D33VS        |

| 2   | VCC_LVDS_SEL |

| 3   | D50VS        |

Table 3-4 LVDS Power Jumper Pin Definition

| Jumper setting (Jumper:P5) | Configuration                      |

|----------------------------|------------------------------------|

| P5 (1-2)                   | Using 3.3V to power the LVDS panel |

| P5 (2-3)                   | Using 5V to power the LVDS panel   |

# 3.2.4 USB client header (P18)

Table 3-5 USB Client Header Pin Definition

| Pin | Signal           |

|-----|------------------|

| 1   | USB power detect |

| 2   | D-               |

| 3   | D+               |

| 4   | GND              |

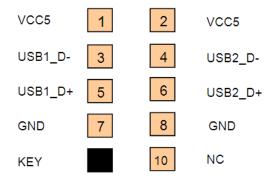

## 3.2.5 **USB Header (P6)**

Table 3-6 USB Header Pin Definition

| Pin | Signal   |

|-----|----------|

| 1   | USB0_PWR |

| 2   | USB1_PWR |

| 3   | USB0_DN  |

| 4   | USB1_DN  |

| 5   | USB0_DP  |

| 6   | USB1_DP  |

| 7   | GND      |

| 8   | GND      |

| 9   | dummy    |

| 10  | NC       |

## 3.2.6 eUSB Header (P2)

Table 3-7 eUSB Pin Header Definition

| Pin | Signal   |

|-----|----------|

| 1   | USB4_PWR |

| 2   | USB5_PWR |

| 3   | USB4_DN  |

| 4   | USB5_DN  |

| 5   | USB4_DP  |

| 6   | USB5_DP  |

| 7   | GND      |

Table 3-7 eUSB Pin Header Definition

| Pin | Signal |

|-----|--------|

| 8   | GND    |

| 9   | dummy  |

| 10  | NC     |

## 3.2.7 Audio Header (P12)

Table 3-8 Audio Header Pin Definition

| Pin | Signal  |

|-----|---------|

| 1   | Dummy   |

| 2   | GND     |

| 3   | Dummy   |

| 4   | NC      |

| 5   | LOUT_R  |

| 6   | Dummy   |

| 7   | GND     |

| 8   | Dummy   |

| 9   | LOUT_L  |

| 10  | LOUT_JD |

## 3.2.8 CAN Bus Header (P15)

Table 3-9 CAN Bus Header Pin Definition

| Pin | Signal |

|-----|--------|

| 1   | CAN_H  |

Table 3-9 CAN Bus Header Pin Definition

| Pin | Signal |

|-----|--------|

| 2   | GND    |

| 3   | CAN_L  |

| 4   | VCC5   |

### 3.2.9 Full Wire RS232 Header (P7)

Table 3-10 Full Wire RS232 Header Pin Definition

| Pin | Signal    |

|-----|-----------|

| 1   | COM1A_DCD |

| 2   | COM1A_RXD |

| 3   | COM1A_TXD |

| 4   | COM1A_DTR |

| 5   | GND       |

| 6   | COM1A_DSR |

| 7   | COM1A_RTS |

| 8   | COM1A_CTS |

| 9   | COM1A_RI- |

## 3.2.10 Two Wire RS232 Header (P14)

Table 3-11 Two Wire RS232 Header

| Pin | Signal       |

|-----|--------------|

| 1   | COM2_RXD_232 |

| 2   | COM2_TXD_232 |

Table 3-11 Two Wire RS232 Header (continued)

| Pin | Signal       |

|-----|--------------|

| 3   | GND          |

| 4   | GND          |

| 5   | COM3_RXD_232 |

| 6   | COM3_TXD_232 |

| 7   | GND          |

| 8   | GND          |

| 9   | COM4_RXD_232 |

| 10  | COM4_RXD_232 |

## 3.2.11 Battery Socket (XBT1)

Table 3-12 Battery Header Pin Definition

| Pin | Signal |

|-----|--------|

| 1   | VBAT   |

| 2   | GND    |

| 3   | VBAT   |

## 3.2.12 Front Panel Header (P19)

Table 3-13 Front Panel Header Pin Definition

| Pin | Signal    |

|-----|-----------|

| 1   | HD_LED    |

| 2   | POWER_LED |

| 3   | HD_LED_N  |

Table 3-13 Front Panel Header Pin Definition

| Pin | Signal |

|-----|--------|

| 4   | GND    |

| 5   | GND    |

| 6   | PWRBTN |

| 7   | RESET  |

| 8   | GND    |

| 9   | Dummy  |

| 10  | KEY    |

## 3.2.13 **GPIO** Header (P4)

Table 3-14 GPIO Header Pin Definition

| Pin | Signal |

|-----|--------|

| 1   | GPO0   |

| 2   | GPI0   |

| 3   | GPO1   |

| 4   | GPI1   |

| 5   | GPO2   |

| 6   | GPI2   |

| 7   | GPO3   |

| 8   | GPI3   |

| 9   | V5S    |

| 10  | GND    |

## 3.2.14 CPU FAN Header (P1)

Table 3-15 CPU FAN Header Pin Definition

| Pin | Signal |

|-----|--------|

| 1   | GND    |

| 2   | D50VS  |

| 3   | TACH   |

| 4   | PWM    |

## 3.2.15 SATA Power Header (P16)

Table 3-16 SATA Power Header Pin Definition

| Pin | Signal |

|-----|--------|

| 1   | +12V   |

| 2   | GND    |

| 3   | +5V    |

| 4   | GND    |

| 5   | +3.3V  |

### 3.2.16 J9 SATA Connector

Table 3-17 J9 SATA Pin Definition

| Pin | Signal   |

|-----|----------|

| S1  | GND      |

| S2  | SATA_TXP |

Table 3-17 J9 SATA Pin Definition (continued)

| Pin | Signal   |

|-----|----------|

| S3  | SATA_TXN |

| S4  | GND      |

| S5  | SATA_RXN |

| S6  | SATA_RXP |

| S7  | GND      |

| P1  | +3.3V    |

| P2  | +3.3V    |

| P3  | +3.3V    |

| P4  | GND      |

| P5  | GND      |

| P6  | GND      |

| P7  | +5V      |

| P8  | +5V      |

| P9  | +5V      |

| P10 | GND      |

| P11 | RESERVED |

| P12 | GND      |

| P13 | +12V     |

| P14 | +12V     |

| P15 | +12V     |

# 3.3 Onboard LEDs

Table 3-18 Onboard LEDs

| Location | Color | Description         |

|----------|-------|---------------------|

| D2       | RED   | Processor Hot Alert |

| D8       | RED   | Thermal Trip Alert  |

| D12      | Green | Power OK indicator  |

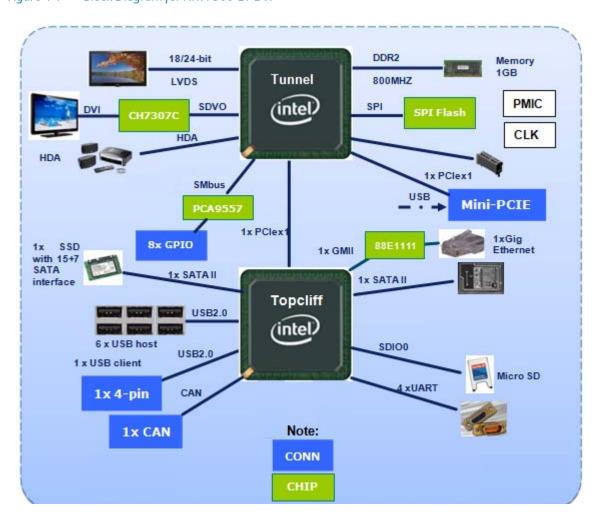

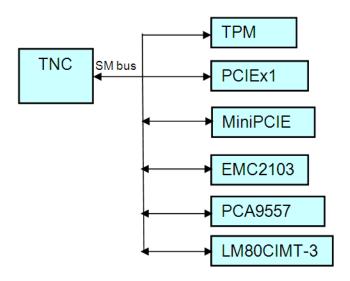

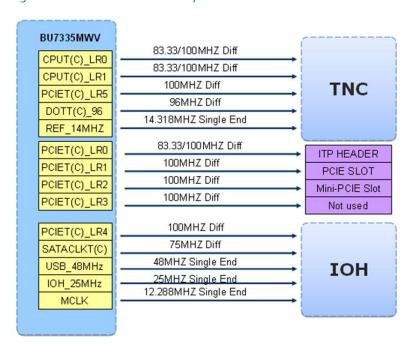

## 4.1 Block Diagram

Figure 4-1 Block Diagram for NITX-300-ET-DVI

## 4.2 Processor

NITX-300-ET-DVI is designed to support the Tunnel Creek processor. The features are detailed in the table below:

Table 4-1 Tunnel Creek Processor Features

| Feature                                                    | Description                                                                                                                                                                                                                                                                                                                      |  |  |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Low-Power Intel Architecture Core                          | 600 MHz (Ultra Low Power SKU), 1.0 GHz (Mainstream SKU) and 1.3 GHz (Premium SKU) with related TDP 2.7, 3.1, 3.3 W                                                                                                                                                                                                               |  |  |